2019年2月21日,自适应和智能计算的全球领先企业赛灵思公司宣布其屡获殊荣的Zynq® UltraScale+™ 射频(RF)片上系统(SoC)产品系列再添新品,具有更高射频(RF)性能及更强可扩展能力。新一代器件建立在 Zynq UltraScale + RFSoC 基础产品系列在多个市场的成功之上,可支持6GHz 以下所有频段,从而满足新一代 5G 部署的关键需求。同时,还可支持针对采样率高达 5GS/S的14位模数转换器(ADC)和10 GS/S的14位数模转换器(DAC)进行直接RF采样,二者的模拟带宽均高达 6GHz。

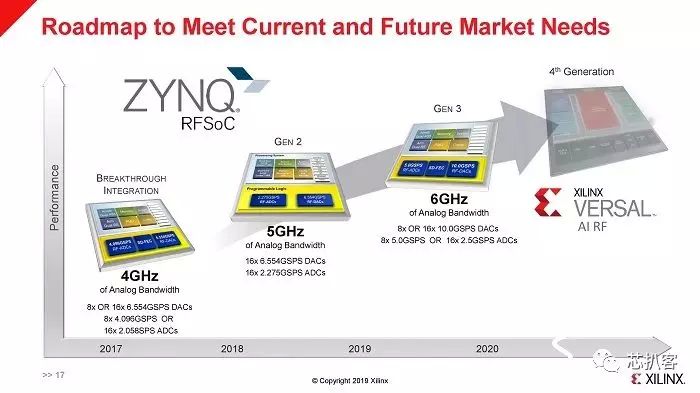

赛灵思 RFSoC 产品系列,是行业唯一一款可满足当前及未来行业需求的单芯片自适应射频平台。该产品系列现在包括:

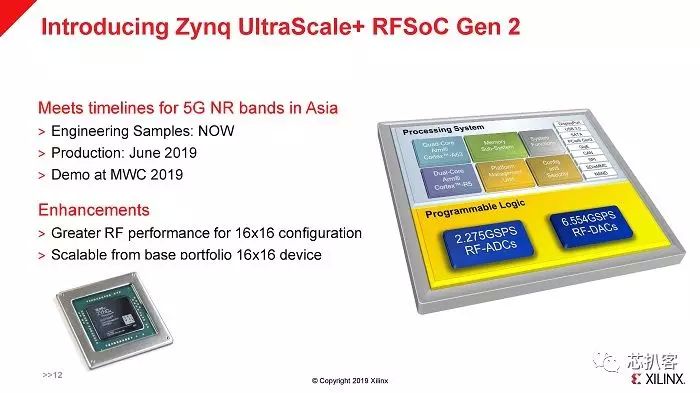

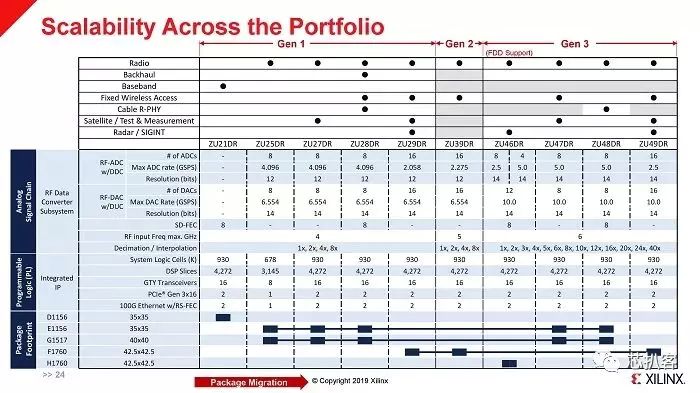

- Xilinx Zynq UltraScale + RFSoC Gen 2 (第二代):这款现已开始提供样片并计划于 2019 年 6 月投入量产的器件,不仅符合亚洲地区5G部署的时间规划,而且还支持最新射频技术。

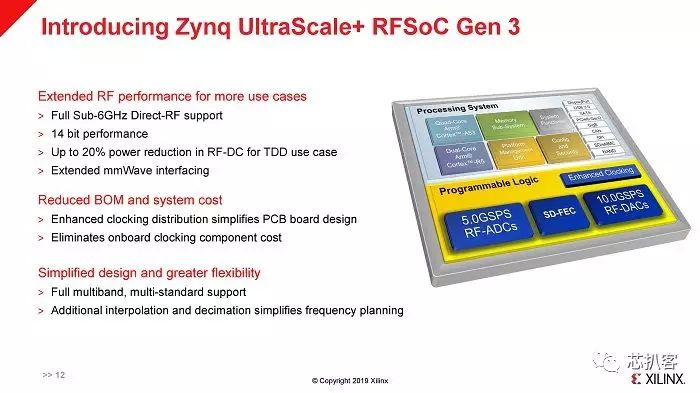

- Xilinx Zynq UltraScale + RFSoC Gen 3 ( 第三代):与基础产品系列相比,可在 RF 数据转换器子系统中对 6Ghz 以下频段直接 RF 采样提供全面支持、扩展的毫米波接口,并将功耗降低达 20%。该产品将于 2019 年下半年上市。

新产品单芯片集成更高性能的 RF 数据转换器,可为部署 5G 无线通信系统、有线电视接入、高级相控阵雷达解决方案,以及包括测量测试和卫星通信在内的其它应用,提供所需的广泛频段覆盖范围。通过取代分立式组件,这些器件可将功耗及封装尺寸锐降 50%,是电信运营商部署5G 系统实现大规模多输入多输出基站的理想选择。

解读下一代 Zynq Ultrascale + RF SoC

与 4G 和 3G 时代一样,5G 网络的建设,需要许多嵌入式无线设备的配合。在技术设施与测试平台的搭建商,通常无法用上现成的所有部件。因其对系统提出了很多的要求,例如灵活性、密度、快速发布、以及可重新配置性。好消息是,赛灵思(Xilinx)于昨日推出了其下一代 Zynq Ultrascale + RF SoC,将数字硬件与模拟模块整合到了单个芯片中。

射频 SoC 是一种单芯片自适应无线电平台,在台积电 16nm 制程的加持下,Xilinx 将其硬件、可编程软件引擎、以及 RF 模拟技术,高密度地整合到了一起。

在前几代产品中,系统需要依靠多个芯片,来执行以下所有任务。但现在,Xilinx 提供了一套极其简化的方案设计,集成了完全的 RF 信号链。

从 MAC 到 DSP、无线 IP、基带、调制、DSP 信令与滤波、ADC / DAC、重头的通用数字处理器、以及 DDR4 内存子系统。

Xilinx 表示,RFSoC 的优势之一,在于面向无线网络的 Massive-MIMO 射频模组。

赛灵思介绍称,在 RFSoC 的帮助下,64×64 m-MIMO 可将功耗降低一半、安装量减少75%、系统组件数量减少 89% 。

新发布的 RFSoC 新品,包括了第二代和第三代产品。在初代产品中,Xilinx 提供了可覆盖 4GHz 频段和 DOCSIS 3.1 的方案,实现了 5G 部署所需的部分定位。

第二代产品,是基于初代快速上市方案的快速战略调整,可覆盖 5GHz 频段,以便在中日等市场尽快投入使用。

第三代产品属于刷新后的设计,可覆盖 6GHz 频段,支持已授权和空白频谱,旨在实现全球范围内的 5G 部署。

不过首先走出大门的,还是第二代产品。如上所述,它是面向亚洲市场的初代调节增强版,有望尽快展开 5G 频段下的测试。

Xilinx 表示,现可向特定客户提供工程样品,并将于 2019 年 6 月全面投产。第三代产品采用了类似的底层硬件(四核 A53 + 带有可编程逻辑的双核 A5 CPU)。

不过还有固定功能的 ADC / DAC 升级,以及在不同时钟域上支持 6GHz 频段、增强可编程逻辑的时钟,特别是对于具有高达 14 位处理的 6GHz 的额外 DSP 要求。

Xilinx 表示,第三代产品将降低 TDD 上的功耗,扩展毫米波接口,以及完整的多频段 / 多标准支持。

增强型时钟还意味着在外部时钟发生器模式下,整个设计只需要一个外部时钟发生器,而不是之前所需的最多四个。

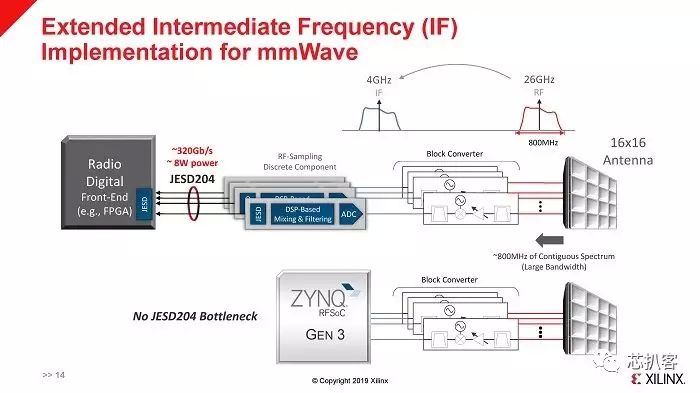

Xilinx 表示,其集成的模拟 / 数字解决方案,还有助于毫米波扩展中频的实施。传统设计的一个问题是,射频采样离散 DSP 和数字前端之间的接口,是一个给定的标准(即 JESD204)。

然而在 16×16 天线方案中,该标准接口在 320 Gb/s 时,功率消耗在 8W 左右。如果需要解析 800 MHz 的高频频谱,功耗就会大增。

通过在第三代产品中整合数字、模拟组件,Xilinx 可在单芯片能完成全部接口工作,从而带来更低的功耗、以及更高速的传输。

该公司声称,Xilinx 声称,其允许一级供应商将它们的定制可编程 IP 与 RF 配套使用。二级供应商也可以使用专属的、或固定的 IP解决方案。

通过该设计,Xilinx 可将 RF 市场添加到其产品组合中。据悉,第三代 RFSoC 将在 2019 下半年开始出样,并在 2020 年三季度开始量产。

至于为何要拖这么久,是因为供应商验证测试的时间表,比我们设想的要更久。该部分将覆盖所有尚未授权的 6GHz一下频段芯片。

需要指出的是,第二代和第三代器件,都将与第一代硬件保持引脚上的兼容。