11月11日,全球领先的IC设计公司联发科技宣布推出通过7nm FinFET硅认证(Silicon-Proven)的112G PAM4远程(LR)SerDes IP芯片,进一步扩大了ASIC的产品线。11月15日,联发科技在深圳办公室举行媒体见面会,向媒体详细介绍了联发科技的ASIC的业务和最新的技术发展方向。

联发科技副总经理徐敬全

联发科技副总经理徐敬全对《芯扒客》记者表示,从2019年的数据统计,物联网终端产生的数据流以超过14个Zettabyte(1ZB=10²¹B)的速度向数据中心汇总,还以每年25%的速度增加,未来物联网设备所需要处理的数据量会更庞大,这将衍生出更多新的芯片需求。这对联发科来讲,是一个非常好的机会。

联发科在积累了足够的IP和客户信赖度后,ASIC成为重要战场,陆续取得微软、索尼、阿里巴巴、思科等重要客户。2019年联发科3月营收上升近6成,在市场不确定性高且手机市场趋缓的情况下,营收的大部分因素有赖于ASIC产品线的稳定增长。“ASIC的需求是长期稳定的,所以它能给公司带来相对稳定且较长期的营收,ASIC相对提供服务的时间很长,比如卖一个ASIC的时间就超过5-7年,甚至更长,所以这个稳定营收的帮助将是更长远且更稳定,跟合作伙伴的关系也将是长期的关系。”徐敬全表示。

联发科打算如何深入市场?

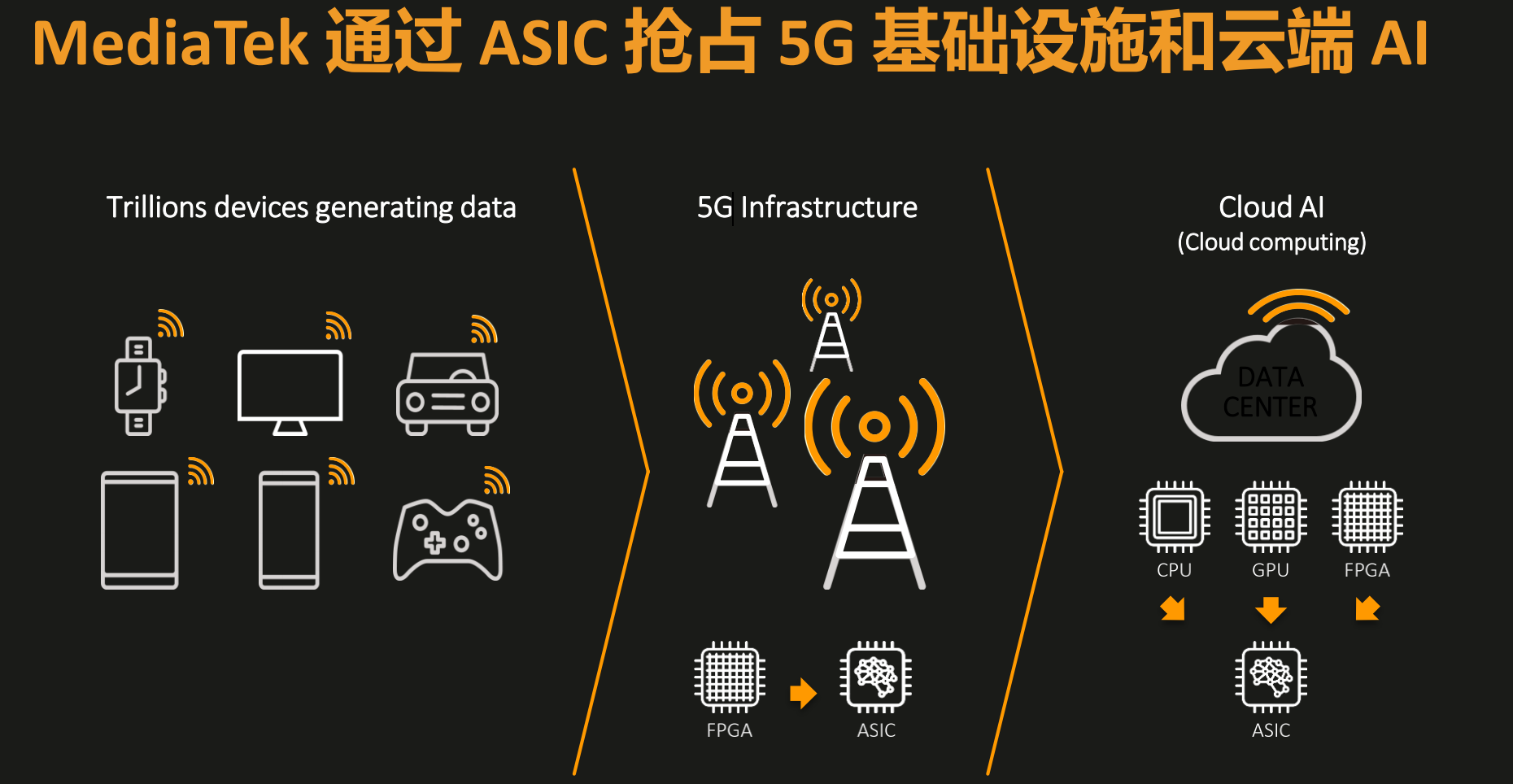

徐敬全表示,过去联发科的产品比较少抓云跟管(管主要指基础设施,比如5G)的机会,物联网和AI的兴起,使得庞大的数据流必须从终端设备经过各种有线、无线的5G基础设施,再带到云端做更多的AI算力处理,让本该属于FPGA机会的市场开始无法被满足,客户更需要客制化的芯片去满足越来越多元化和差异化的用户需求。

在AIoT时代,数据中心对高速处理单元和AI处理的渴求,让ASIC芯片逐渐有底气和FPGA抢夺云端AI和5G基础设施的市场。

FPGA属于半定制芯片,最大的优势是用户不需要改变硬件,就可以通过升级软件来配置这些芯片并实现自定义硬件功能。“随着时间往下走,会有一部分原来FPGA被做成客制化的芯片,另一小部分的FPGA还在原来的系统里去处理一些需要弹性应用的需求,所以我们的预测是,FPGA和ASIC都会持续成长,长期共存,谁也不能取代谁。”徐敬全表示。

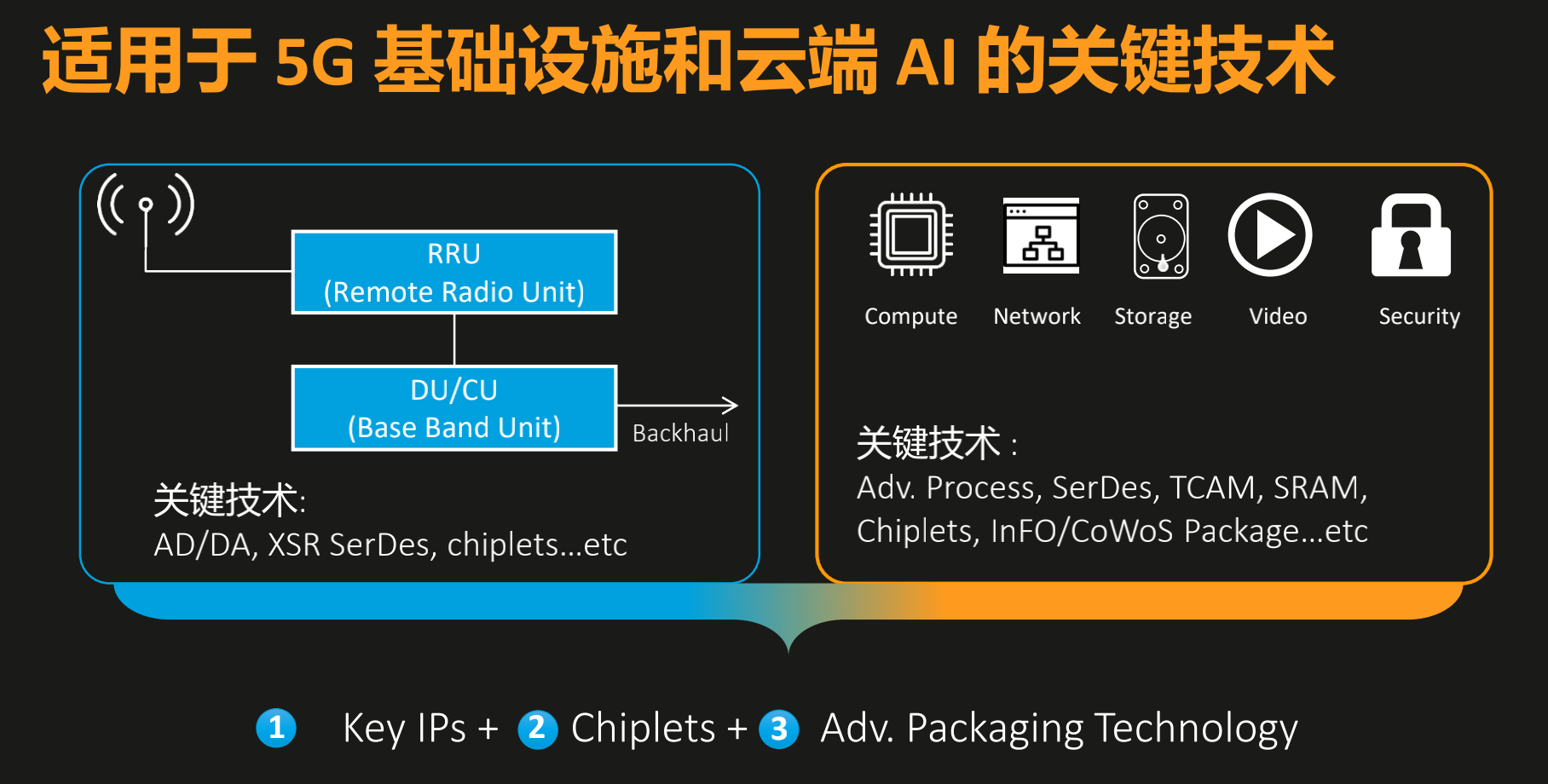

4G运营商在部署网络初期,量还不够大,采用FPGA就能满足市场的要求。随着5G基础设施的完善和数据中心的规模化,FPGA的速度和功耗问题开始跟不上,而且5G基站的建设比4G基站更加密集和复杂,基站业者通过Remote Radio Unit把原先的RF信号处理器进行数位变动,转化成数位化传送到后面的基频、基站部分,再通过基频的处理把信号传输到数据中心,在这巨大且高频的处理过程中,需要高速的Ultra-shortrange SerDes把这些高速的芯片串接起来。

还有云端数据中心产生的不同需求,用我们常见的CPU、GPU以及半定制的FPGA都不能高效的贴合要求,ASIC芯片的计算能力和计算效率可以直接根据特定算法的需求进行定制,能实现体积小、功耗低、可靠性高、保密性好、计算能力强、计算效率高等优势。

并不是所有要做IC的公司都是联发科的潜在客户,徐敬全表示,过去联发科接的比较多的是按照客户的需求去设计IC,现在更多是客户把自己关键IP技术融合在要设计的IC中,其中5G的基础设施和领先的云端AI技术、网络相关的芯片等,都会是联发科着力发展的应用领域,联发科会在这几个领域去筛选最领先的客户,除此之外还有策略上的布局以及考虑。

联发科的ASIC将锁定哪些市场?

前面提到的5G的基础建设和云端AI,是联发科ASIC业务的重点市场之一。徐敬全认为,对联发科来说,大型的数据中心会是下一波产业的革命。他表示,从具体的产品布局来看,联发科的布局将集中在AI加速器、数据中心的路由器和交换器的芯片、5G基站、以及背后的网络传输芯片等方向。

联发科为何能在众多ASIC公司中突出重围?

联发科技过去20多年SoC的经验,积累了大量的关键IP,如高速的Serdes,以及存储(DCAN,很独特的IP,全世界目前能做到这么高速的DCAN不会超过3家,可以做到1Ghz),先进制程和low power的经验。

“要抓取5G的基础建设和云端AI相关应用里的芯片机会,需要关键的IP、芯粒(chiplets)、先进的封装技术做支撑,联发科到底在这样的机会里有什么优势?”联发科技副总经理徐敬全表示主要分四个领域:

第一是IP技术的完整性。做成一颗IC芯片需要各种各样不同的IP,不同客户有不同的开发需求,就涉及到不同的IP需求。很多IC设计公司没有底层的IP,联发科过去在智能手机、安卓平板、数字电视、网络连接等领域积累了大量的IP,其中还包含了SerDes、TCAM、SRAM、ADDA等关键技术。

第二是先进制程的领先性。不管是5G的基础设施和云端数据中心的芯片,所有的应用都需要最先进制程做背书。很多公司难以投入巨量资金跟进工艺研发,而联发科一直跟随工艺的脚步掌握最领先的工艺制程,包括现在最新的7nm制程,以及接下来最先进的制程。“一个7nm的光罩就要7000万人民币,目前5nm已经是天价的数字,所以先进制程不光是砸钱,它还需要一个经济规模来支撑先进制程的开发,像联发科等大型公司才有能力跟技术继续往先进技术去做下一代的发展,这也是联发科的优势所在。”徐敬全表示。

目前联发科可以做到的最大封装已经接近100mm*100mm,把芯片做大意味着它的复杂度和技术门槛提高了。尤其是技术门槛方面,要保证IC不会随便动一下就脆化掉,或者在IC封装时因脆化导致平整度的问题,这对封装技术的要求又提高了。

第三是丰富的设计经验。联发科一直从事SoC芯片的研发,而且一款芯片从设计到工艺制造、封装测试、终端应用,涉及非常多的环节,每个环节都要有关键IP和丰富的技术经验做支持。因此有系统、有效率的提供IC设计流程跟方法显得尤为重要。

第四是产品的质量保证。联发科每年累积的芯片出货量超过15亿颗,通过重重筛选最后到终端消费者上,所以它的瑕疵率是很低的,在品质管控上有所保障。其次,联发科还跟台积电等重要先进制程的晶圆代工厂有非常密切的合作关系,陆陆续续还会往前推进,包括highspeed SerDes,ADDA转换等IP,还有InFO/CoWoS的技术,以及先进技术的投资。

这里要重点介绍一下联发科新推出的技术IP,通过7nm FinFET硅认证(Silicon-Proven)的112G PAM4远程(LR)SerDesIP芯片。SerDes产品组合可以为 ASIC芯片设计提供从10G、28G、56G到 112G等多种解决方案。

联发科的112G远程SerDes是基于高性能DSP的解决方案,具有PAM4和NRZ信令,适用于恶劣环境与嘈杂的应用场景。此外,112GLR SerDes支持多种IEEE标准速度,包括1/10/25/50/100G和FC16/FC32/FC64。

在5G和AI双管齐下的大数据时代,传输前比如首先通过服务器将数据转换成一个串列数,所以未来数据中心的运算能力和运算速度关键有赖于SerDes的快慢,影响数据传输和接收的速度。

“此次的112G SerDes相比56G的是SerDes,虽然同样是PAM4的架构,但在速度上提升了一倍,面积增加了1.3倍,性能提升了1.5倍。除了传输和接收性能优异外,我们采取的一个架构对温度做了特别的设计,对高温的控制比业界标准要高出1-2个级别,尤其是应对户外5G基站设施恶劣的温差变化,可以降低传输数据时产生的百分之一,甚至十分之一的错误率。”徐敬全表示。

据了解,联发科技从2011年就开始10~112G SerDes的开发,并且逐渐追赶上全球最先进的几家供应商。联发科的ASIC业务已涉及企业和超大规模数据中心、超高性能网络交换机、路由器或计算应用、gNB(5G)基础架构、AI/DL应用,要求在长距离互连中具备极高带宽的新型计算应用等众多领域。联发科似乎在ASIC业务上押注越来越大的筹码,尤其是5G和AI数据中心的市场,随着5G和AI的爆发,未来联发科ASIC业务或将成为与联发科手机业务并驾齐驱的一大业务。